What is Chip Scale Package (CSF)

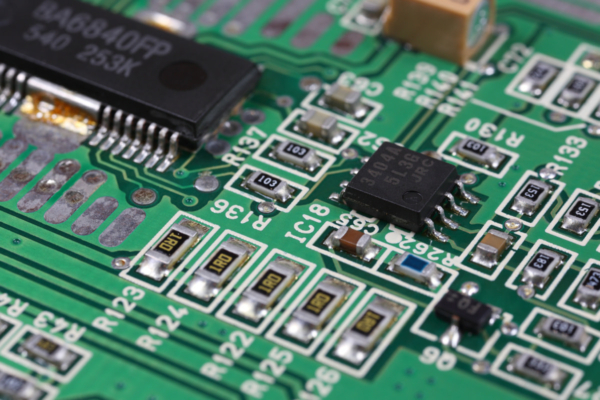

A Chip scale package (CSP) is a type of integrated circuit package characterized by its small size and direct surface mountability. The term “chip-scale package” is somewhat misleading, as not all packages labeled as CSPs are actually the size of a chip. Instead, the definition provided by IPC/JEDEC is used to determine whether a package can be classified as a chip-scale package. According to this definition, a CSP must have an area no greater than 1.2 times that of the die and must be a single-die, direct surface mountable package. Additionally, the ball pitch of the CSP should be no more than 1mm.

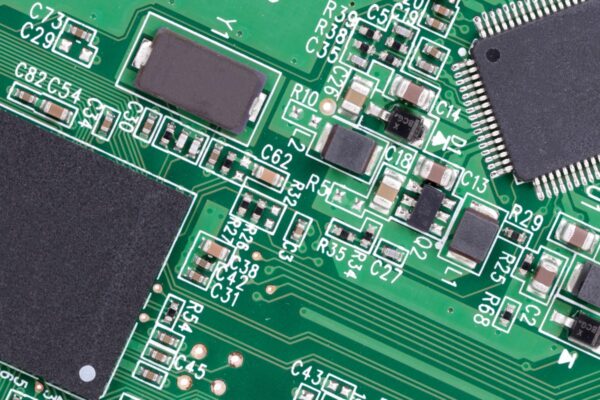

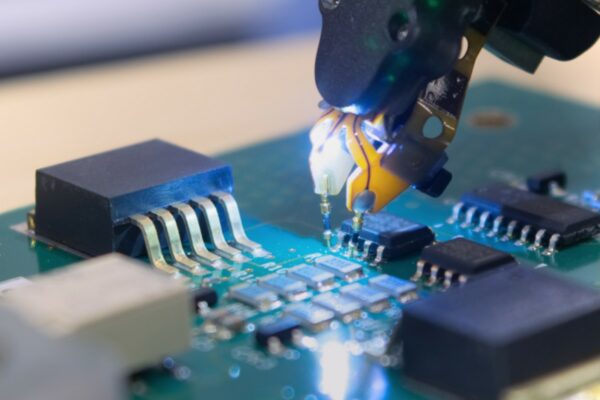

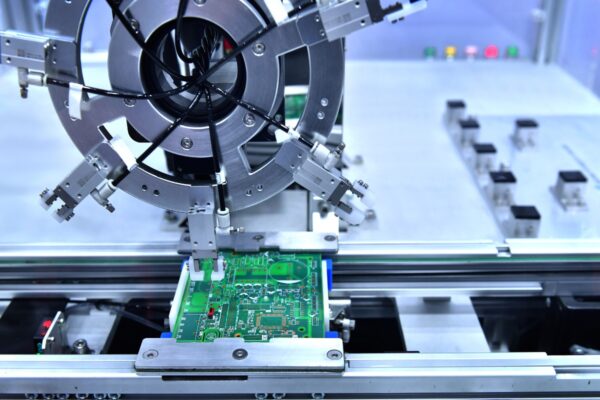

CSPs offer several benefits, including size reduction compared to traditional packages, weight reduction in electronic devices, self-alignment characteristics, and compatibility with existing surface mount technology (SMT). They are widely used in electronic devices such as cell phones, smart devices, laptops, and digital cameras. CSPs can be mounted on an interposer or have the pads directly etched or printed onto the silicon wafer, resulting in a wafer-level package (WLP) or wafer-level chip-scale package (WL-CSP). The concept of CSP was first proposed in 1993 and has since become one of the biggest trends in the electronics industry.